### The Free Lunch

## 27. Parallel Programming I

Moore's Law und The Free Lunch, Hardware Architekturen, Parallele Ausführung, Klassifikation nach Flynn, Multi-Threading, Parallelität und Nebenläufigkeit, Skalierbarkeit: Amdahl und Gustafson, Datenund Taskparallelität, Scheduling

[Task-Scheduling: Cormen et al, Kap. 27]

The free lunch is over <sup>36</sup>

<sup>36</sup>"The Free Lunch is Over", a fundamental turn toward concurrency in software, Herb Sutter, Dr. Dobb's Journal, 2005

771

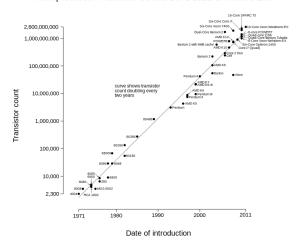

### Moore's Law

Beobachtung von Gordon E. Moore:

Die Anzahl Transistoren in integrierten Schaltkreisen verdoppelt sich ungefähr alle zwei Jahre.

### Moore's Law

### Microprocessor Transistor Counts 1971-2011 & Moore's Law

SBy Wgsimon, https://commons.wikimedia.org/w/index.php?curid≡

### Für eine lange Zeit...

Heute

- wurde die sequentielle Ausführung schneller (Instruction Level Parallelism, Pipelining, Höhere Frequenzen)

- mehr und kleinere Transistoren = mehr Performance

- Programmierer warteten auf die nächste schnellere Generation

- steigt die Frequenz der Prozessoren kaum mehr an (Kühlproblematik)

- steigt die Instruction-Level Parallelität kaum mehr an

- ist die Ausführungsgeschwindigkeit in vielen Fällen dominiert von Speicherzugriffszeiten (Caches werden aber immer noch grösser und schneller)

775

### **Trends**

# Dual-Core Itanium 2 1,000,000 Intel CPU Trends (sources: Intel. Wikipedia, K. Olukotun) 100.000

### **Multicore**

- Verwende die Transistoren für mehr Rechenkerne

- Parallelität in der Software

- Implikation: Programmierer müssen parallele Programme schreiben, um die neue Hardware vollständig ausnutzen zu können

### Formen der Parallelen Ausführung

- Vektorisierung

- Pipelining

- Instruction Level Parallelism

- Multicore / Multiprocessing

- Verteiltes Rechnen

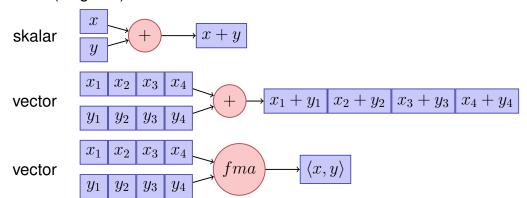

### **Vektorisierung**

Parallele Ausführung derselben Operation auf Elementen eines Vektor(Register)s

779

### Hausarbeit

### Effizienter

### **Pipeline**

### Time T3 T4 T5 T6 T7 T8 T2 I0 S0 S1 52 **S**3 I1 S0 S1 S2 S3 I2 S1 S2 S3 I3 S1 S2 S3 14 S2 S3 **I**5 S0 S1 S2 S3 16 S0 S1 S2 S3 Lead In Full Utilization Lead out

### **Throughput (Durchsatz)**

- Throughput = Rate der ein- oder ausgehenden Daten

- Anzahl Operationen pro Zeiteinheit

- Je grösser, desto besser

- Approximation

$$throughput = \frac{1}{\max(Berechnungszeit(Stufen))}$$

ignoriert lead-in und lead-out Zeiten

783

### Latenz

- Zeit zum Ausführen einer Berechnung

- Pipeline-Latenz ist nur konstant, wenn die Pipeline balanciert ist: Summe aller Operationen über die Stufen

- Unbalancierte Pipeline

- Erster Durchlauf wie bei der balancierten Pipeline

- $\blacksquare \ \, \textbf{Balancierte Version}, \ \, \textbf{Latenz} = \# stufen \cdot \max(Berechnungszeit(Stufen))$

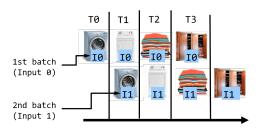

### **Beispiel Hausarbeit**

Waschen  $T_0=1h$ , Trocknen  $T_1=2h$ , Bügeln  $T_2=1h$ , Versorgen  $T_3=0.5h$

- Latenz Erster Durchlauf:  $L = T_0 + T_1 + T_2 + T_3 = 4.5h$

- Latenz Zweiter Durchlauf:  $L = T_1 + T_1 + T_2 + T_3 = 5.5h$

- Langfristiger Durchsatz: 1 Ladung alle 2h (0.5/h).

785

### Throughput vs. Latency

- Erhöhen des Throughputs kann Latenz erhöhen

- Stufen der Pipeline müssen kommunizieren und synchronisieren: Overhead

### **Pipelines in CPUs**

Fetch

Decode

Execute

Data Fetch

Writeback

### Mehrere Stufen

- Jede Instruktion dauert 5 Zeiteinheiten (Zyklen)

- Im besten Fall: 1 Instruktion pro Zyklus, nicht immer möglich ("stalls")

Parallelität (mehrere funktionale Einheiten) führt zu schnellerer Ausführung.

787

78

### ILP - Instruction Level Parallelism

Moderne CPUs führen unabhängige Instruktionen intern auf mehreren Einheiten parallel aus

- Pipelining

- Superscalar CPUs (multiple instructions per cycle)

- Out-Of-Order Execution (Programmer observes the sequential execution)

- Speculative Execution

### 27.2 Hardware Architekturen

### Gemeinsamer vs. verteilter Speicher

# Gemeinsamer Speicher CPU CPU CPU CPU CPU CPU CPU Mem Mem Mem Mem Mem Interconnect

### **Shared vs. Distributed Memory Programming**

- Kategorien des Programmierinterfaces

- Kommunikation via Message Passing

- Kommunikation via geteiltem Speicher

- Es ist möglich:

- Systeme mit gemeinsamen Speicher als verteilte Systeme zu programmieren (z.B. mit Message Passing Interface MPI)

- Systeme mit verteiltem Speicher als System mit gemeinsamen Speicher zu programmieren (z.B. Partitioned Global Address Space PGAS)

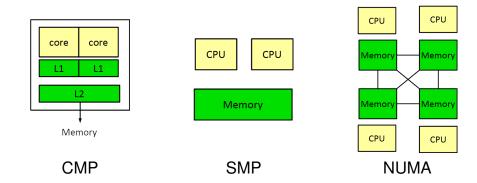

### Architekturen mit gemeinsamen Speicher

- Multicore (Chip Multiprocessor CMP)

- Symmetric Multiprocessor Systems (SMP)

- Simultaneous Multithreading (SMT = Hyperthreading)

- ur ein physischer Kern, Mehrere Instruktionsströme/Threads: mehrere virtuelle Kerne

- Zwischen ILP (mehrere Units für einen Strom) und Multicore (mehrere Units für mehrere Ströme). Limitierte parallele Performance

- Non-Uniform Memory Access (NUMA)

Gleiches Programmierinterface!

### Übersicht

791

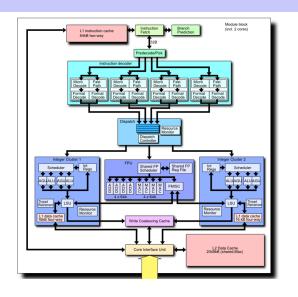

### **Ein Beispiel**

AMD Bulldozer: Zwischen CMP und SMT

- 2x integer core

- 1x floating point core

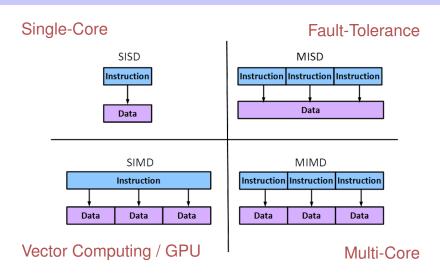

### Klassifikation nach Flynn

**Massiv Parallele Hardware**

[General Purpose] Graphical Processing Units ([GP]GPUs)

- Revolution im High Performance Computing

- Calculation 4.5 TFlops vs. 500 GFlops

- Memory Bandwidth 170 GB/s vs. 40 GB/s

- SIMD

- Hohe Datenparallelität

- Benötigt eigenes Programmiermodell.Z.B. CUDA / OpenCL

27.3 Multi-Threading, Parallelität und Nebenläufigkeit

### **Prozesse und Threads**

### Warum Multithreading?

- Prozess: Instanz eines Programmes

- jeder Prozess hat seinen eigenen Kontext, sogar eigenen Addresraum

- OS verwaltet Prozesse (Resourcenkontrolle, Scheduling, Synchronisierung)

- Threads: Ausführungsfäden eines Programmes

- Threads teilen sich einen Addressraum

- Schneller Kontextwechsel zwischen Threads

Thread 3

- Verhinderung vom "Polling" auf Resourcen (Files, Netwerkzugriff, Tastatur)

- Interaktivität (z.B. Responsivität von GUI Programmen)

- Mehrere Applikationen / Clients gleichzeitig instanzierbar

- Parallelität (Performanz!)

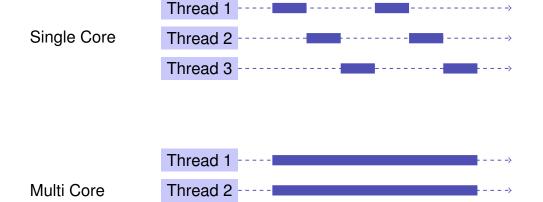

### **Multithreading konzeptuell**

### **Threadwechsel auf einem Core (Preemption)**

801

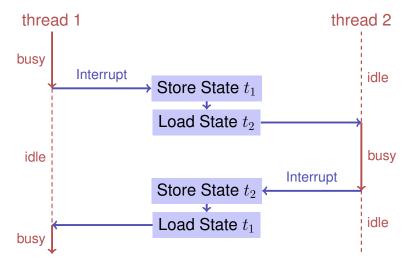

### Parallelität vs. Nebenläufigkeit (Concurrency)

- Parallelität: Verwende zusätzliche Resourcen (z.B. CPUs), um ein Problem schneller zu lösen

- Nebenläufigkeit: Vewalte gemeinsam genutzte Resourcen (z.B. Speicher) korrekt und effizient

- Begriffe überlappen offensichtlich. Bei parallelen Berechnungen besteht fast immer Synchronisierungsbedarf.

### **Thread-Sicherheit**

Thread-Sicherheit bedeutet, dass in der nebenläufigen Anwendung eines Programmes dieses sich immer wie gefordert verhält.

Viele Optimierungen (Hardware, Compiler) sind darauf ausgerichtet, dass sich ein *sequentielles* Programm korrekt verhält.

Nebenläufige Programme benötigen für ihre Synchronisierungen auch eine Annotation, welche gewisse Optimierungen selektiv abschaltet

### **Beispiel: Caches**

- Speicherzugriff auf Register schneller als auf den gemeinsamen Speicher

- Prinzip der Lokalität

- Verwendung von Caches (transparent für den Programmierer)

Ob und wie weit die Cache-Kohärenz sichergestellt wird ist vom eingesetzen System abhängig.

27.4 Skalierbarkeit: Amdahl und Gustafson

### Skalierbarkeit

### **Parallele Performanz**

In der parallelen Programmierung:

- Geschwindigkeitssteigerung bei wachsender Anzahl p Prozessoren

- Was passiert, wenn  $p \to \infty$ ?

- Linear skalierendes Programm: Linearer Speedup

Gegeben fixierte Rechenarbeit W (Anzahl Rechenschritte)

Sequentielle Ausführungszeit sei  $T_1$

Parallele Ausführungszeit  $T_p$  auf p CPUs

- Perfektion:  $T_p = T_1/p$

- Performanzverlust:  $T_p > T_1/p$  (üblicher Fall)

- Hexerei:  $T_p < T_1/p$

### **Paralleler Speedup**

Paralleler Speedup  $S_p$  auf p CPUs:

$$S_p = \frac{W/T_p}{W/T_1} = \frac{T_1}{T_p}.$$

- Perfektion: Linearer Speedup  $S_p = p$

- Verlust: sublinearer Speedup  $T_p > T_1/p$  (der übliche Fall)

- Hexerei: superlinearer Speedup  $T_p < T_1/p$

Effizienz: $E_p = S_p/p$

### **Erreichbarer Speedup?**

Paralleles Programm

| Paralleler Teil | Seq. Teil |

|-----------------|-----------|

| 80%             | 20%       |

$$T_1 = 10$$

$T_8 = ?$

$$T_8 = \frac{10 \cdot 0.8}{8} + 10 \cdot 0.2 = 1 + 2 = 3$$

$$S_8 = \frac{T_1}{T_1} = \frac{10}{9} = 3.33$$

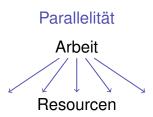

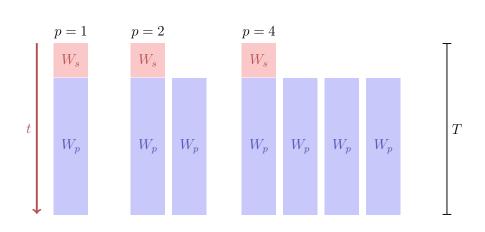

### Amdahl's Law: Zutaten

### Amdahl's Law

Zu Leistende Rechenarbeit W fällt in zwei Kategorien

- $\blacksquare$  Parallelisierbarer Teil  $W_p$

- lacktriangle Nicht paralleliserbarer, sequentieller Teil  $W_s$

Annahme: W kann mit einem Prozessor in W Zeiteinheiten sequentiell erledigt werden ( $T_1 = W$ ):

$$T_1 = W_s + W_p$$

$$T_p \ge W_s + W_p/p$$

$S_p = \frac{T_1}{T_p} \le \frac{W_s + W_p}{W_s + \frac{W_p}{p}}$

811

### Amdahl's Law

Mit seriellem, nicht parallelisierbaren Anteil  $\lambda$ :  $W_s = \lambda W$ ,  $W_p = (1 - \lambda)W$ :

$$S_p \le \frac{1}{\lambda + \frac{1-\lambda}{p}}$$

Somit

$$S_{\infty} \le \frac{1}{\lambda}$$

### Illustration Amdahl's Law

$T_1$

### Amdahl's Law ist keine gute Nachricht

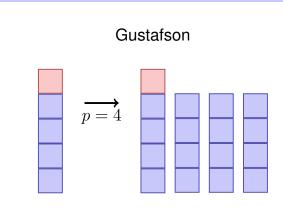

### **Gustafson's Law**

Alle nicht parallelisierbaren Teile können Problem bereiten und stehen der Skalierbarkeit entgegen.

- Halte die Ausführungszeit fest.

- Variiere die Problemgrösse.

- Annahme: Der sequentielle Teil bleibt konstant, der parallele Teil wird grösser.

**Illustration Gustafson's Law**

### **Gustafson's Law**

Arbeit, die mit einem Prozessor in der Zeit T erledigt werden kann:

$$W_s + W_p = T$$

Arbeit, die mit p Prozessoren in der Zeit T erledigt werden kann:

$$W_s + p \cdot W_p = \lambda \cdot T + p \cdot (1 - \lambda) \cdot T$$

Speedup:

$$S_p = \frac{W_s + p \cdot W_p}{W_s + W_p} = p \cdot (1 - \lambda) + \lambda$$

$$= p - \lambda(p - 1)$$

### Amdahl vs. Gustafson

# Amdahl p = 4

### 27.5 Task- und Datenparallelität

819

### Paradigmen der Parallelen Programmierung

## **Beispiel Data Parallel (OMP)**

- Task Parallel: Programmierer legt parallele Tasks explizit fest.

- *Daten-Parallel:* Operationen gleichzeitig auf einer Menge von individuellen Datenobjekten.

```

double sum = 0, A[MAX];

#pragma omp parallel for reduction (+:ave)

for (int i = 0; i < MAX; ++i)

sum += A[i];

return sum;</pre>

```

### **Beispiel Task Parallel (C++11 Threads/Futures)**

```

double sum(Iterator from, Iterator to)

{

auto len = from - to;

if (len > threshold){

auto future = std::async(sum, from, from + len / 2);

return sumS(from + len / 2, to) + future.get();

}

else

return sumS(from, to);

}

```

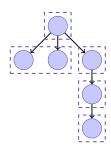

### **Partitionierung und Scheduling**

- Aufteilung der Arbeit in parallele Tasks (Programmierer oder System)

- Ein Task ist eine Arbeitseinheit

- Frage: welche Granularität?

- Scheduling (Laufzeitsystem)

- Zuweisung der Tasks zu Prozessoren

- Ziel: volle Resourcennutzung bei wenig Overhead

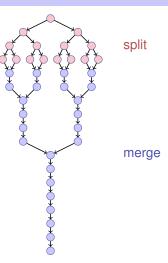

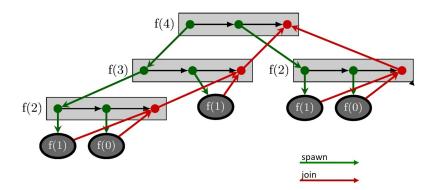

# Beispiel: Fibonacci P-Fib

```

\begin{array}{l} \textbf{if} \ n \leq 1 \ \textbf{then} \\ \quad | \ \textbf{return} \ n \\ \textbf{else} \\ \quad | \ x \leftarrow \textbf{spawn} \ \text{P-Fib}(n-1) \\ \quad y \leftarrow \textbf{spawn} \ \text{P-Fib}(n-2) \\ \quad \text{sync} \\ \quad | \ \textbf{return} \ x + y; \end{array}

```

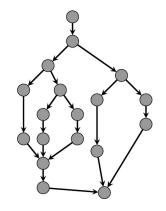

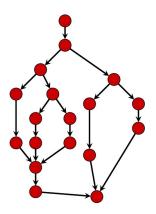

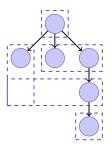

### P-Fib Task Graph

823

Ω

### P-Fib Task Graph

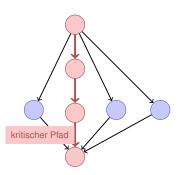

### Frage

827

- Jeder Knoten (Task) benötigt 1 Zeiteinheit.

- Pfeile bezeichnen Abhängigkeiten.

- Minimale Ausführungseinheit wenn Anzahl Prozessoren =  $\infty$ ?

### Performanzmodell

- p Prozessoren

- Dynamische Zuteilung

- $lacktriangleq T_p$ : Ausführungszeit auf p Prozessoren

### Performanzmodell

- $\blacksquare$   $T_p$ : Ausführungszeit auf p Prozessoren

- *T*<sub>1</sub>: *Arbeit:* Zeit für die gesamte Berechnung auf einem Prozessor

- $\blacksquare T_1/T_p$ : Speedup

### Performanzmodell

- $T_{\infty}$ : Zeitspanne: Kritischer Pfad. Ausführungszeit auf  $\infty$  Prozessoren. Längster Pfad von der Wurzel zur Senke.

- $T_1/T_\infty$ : *Parallelität:* breiter ist besser

- Untere Grenzen

$T_p \geq T_1/p$  Arbeitsgesetz  $T_p \geq T_\infty$  Zeitspannengesetz

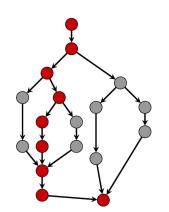

### **Greedy Scheduler**

Greedy Scheduler: teilt zu jeder Zeit so viele Tasks zu Prozessoren zu wie möglich.

### **Theorem**

Auf einem idealen Parallelrechner mit p Prozessoren führt ein Greedy-Scheduler eine mehrfädige Berechnung mit Arbeit  $T_1$  und Zeitspanne  $T_{\infty}$  in Zeit

$$T_p \leq T_1/p + T_{\infty}$$

aus.

831

# Beispiel

Annahme p=2.

$$T_p = 5$$

$$T_p = 4$$

### **Beweis des Theorems**

Annahme, dass alle Tasks gleich viel Arbeit aufweisen.

- Vollständiger Schritt: p Tasks stehen zur Berechnung bereit

- Unvollständiger Schritt: weniger als p Tasks bereit.

Annahme: Anzahl vollständige Schritte grösser als  $\lfloor T_1/p \rfloor$ . Ausgeführte Arbeit  $\geq P \cdot (\lfloor T_1/p \rfloor \cdot p) = T_1 - T_1 \mod p + p \geq T_1$ . Widerspruch. Also maximal  $\lfloor T_1/p \rfloor$  vollständige Schritte.

Jeder unvollständige Schritt führt zu jedem Zeitpunkt alle vorhandenen Tasks t mit  $\deg^-(t)=0$  aus und verringert die Länge der Zeitspanne. Andernfalls wäre die gewählte Zeitspanne nicht maximal. Anzahl unvollständige Schritte also maximal  $T_\infty$ .

### Konsequenz

Wenn  $p \ll T_1/T_{\infty}$ , also  $T_{\infty} \ll T_1/p$ , dann  $T_p \approx T_1/p$ .

### Beispiel Fibonacci

$T_1(n)/T_\infty(n) = \Theta(\phi^n/n)$ . Für moderate Grössen von n können schon viele Prozessoren mit linearem Speedup eingesetzt werden.

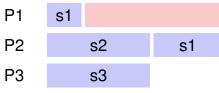

### **Granularität: Wie viele Tasks?**

- #Tasks = #Cores?

- Problem: wenn ein Core nicht voll ausgelastet werden kann

- Beispiel: 9 Einheiten Arbeit. 3 Cores. Scheduling von 3 sequentiellen Tasks.

Exklusive Auslastung:

| P1 | s1 |

|----|----|

| P2 | s2 |

| P3 | s3 |

Ausführungszeit: 3 Einheiten

Fremder Thread "stört":

Ausführungszeit: 5 Einheiten

### **Granularität: Wie viele Tasks?**

- #Tasks = Maximum?

- Beispiel: 9 Einheiten Arbeit. 3 Cores. Scheduling von 9 seguentiellen Tasks.

Exklusive Auslastung:

P1

s1

s4

s7

P2

s2

s5

s8

P3

s3

s6

s9

Ausführungszeit:  $3+\varepsilon$  Einheiten

Fremder Thread "stört":

P1 s1 P2 s2 s4 s5 s8 P3 s3 s6 s7 s9

Ausführungszeit: 4 Einheiten. Volle Auslastung.

### **Granularität: Wie viele Tasks?**

- #Tasks = Maximum?

- Beispiel: 10<sup>6</sup> kleine Einheiten Arbeit.

Ausführungszeit: dominiert vom Overhead.

### **Granularität: Wie viele Tasks?**

Beispiel: Parallelität von Mergesort

Antwort: so viele Tasks wie möglich mit sequentiellem Cut-off, welcher den Overhead vernachlässigen lässt.

- Arbeit (sequentielle Laufzeit) von Mergesort  $T_1(n) = \Theta(n \log n)$ .

- $\blacksquare \ \operatorname{Span} \, T_\infty(n) = \Theta(n)$

- Parallelität  $T_1(n)/T_\infty(n) = \Theta(\log n)$  (Maximal erreichbarer Speedup mit  $p=\infty$  Prozessoren)