## System Construction

Autumn Semester 2015

Felix Friedrich

- Competence in building custom system software from scratch

- Understanding of "how it really works" behind the scenes across all levels

- Knowledge of the approach of fully managed lean systems

A lot of this course **is about detail.** A lot of this course is about **bare metal programming**.

- Discussing elaborated case studies

- In theory (lectures)

- and practice (hands-on lab)

- Learning by example vs. presenting topics

## Prerequisite

- Knowledge corresponding to lectures

Systems Programming and/or Operating

Systems

- Do you know what a stack-frame is?

- Do you know how an interrupt works?

- Do you know the concept of virtual memory?

- Good reference for recapitulation:

*Computer Systems A Programmer's Perspective*

## Links

#### SVN repository

https://svn.inf.ethz.ch/svn/lecturers/vorlesungen/trunk/syscon/2015/shared

Links on the course homepage

http://lec.inf.ethz.ch/syscon/2015

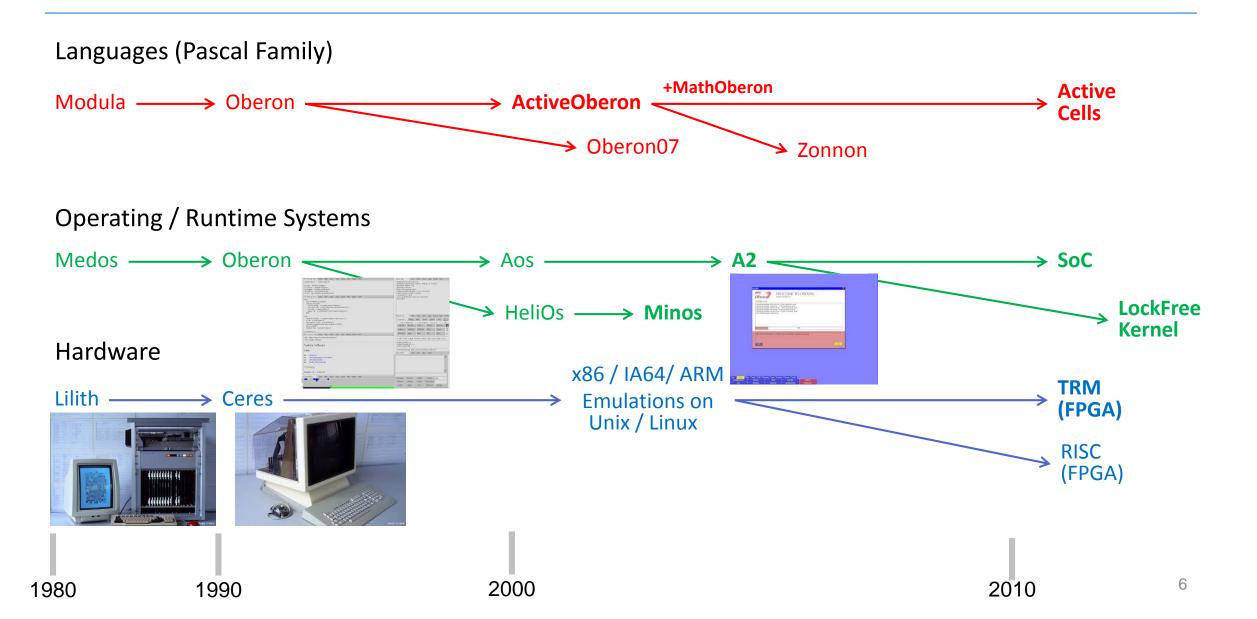

## Background: Co-Design @ ETH

## **Course Overview**

Part1: Contemporary Hardware

## Case Study 1. Minos: Embedded System

- Safety-critical and fault-tolerant monitoring system

- Originally invented for autopilot system for helicopters

- Topics: ARM Architecture, Cross-Development, Object Files and Module Loading, Basic OS Core Tasks (IRQs, MMUs etc.), Minimal Single-Core OS: Scheduling, Device Drivers, Compilation and Runtime Support.

## **Course Overview**

Part1: Contemporary Hardware

### Case Study 2. A2: Multiprocessor OS

- Universal operating system for symmetric multiprocessors (SMP)

- Based on the co-design of a programming language (Active Oberon) and operating system (A2)

- Topics: Intel SMP Architecture, Multicore Operating System, Scheduling, Synchronisation, Synchronous and Aysynchronous Context Switches, Priority Handling, Memory Handling, Garbage Collection.

#### Case Study 2a: Lock-free Operating System Kernel

With hands-on labs on x86ish hardware and Raspberry Pi

## **Course Overview**

Part2: Custom Designed Systems

#### Case Study 3. RISC: Single-Processor System

- RISC single-processor system designed from scratch: hardware on FPGA

- Graphical workstation OS and compiler ("Project Oberon")

- Topics: building a system from scratch, Art of simplicity, Graphical OS, Processor Design.

#### Case Study 4. Active Cells: Multi-Processor System

- Special purpose heterogeneous system on a chip (SoC)

- Massively parallel hard- and software architecture based on Message Passing

- Topics: Dataflow-Computing, Tiny Register Machine: Processor Design Principles, Software-/Hardware Codesign, Hybrid Compilation, Hardware Synthesis

## Organization

Lecture Tuesday 13:15-15:00 (CAB G 57) with a break around 14:00

Exercise Lab Tuesday 15:00 – 17:00 (CAB G 56)

Guided, open lab, duration normally 2h

First exercise: today (15th September)

Oral Examination in examination period after semester (15 minutes).

Prerequisite: knowledge from both course and lab

## Design Decisions: Area of Conflict

| simple /<br>undersized           |                      | sophisticated /<br>complex      |

|----------------------------------|----------------------|---------------------------------|

| tailored /<br>non-generic        | Programming Model    | universal /<br>overly generic   |

| comprehensible /<br>simplicistic | Compiler<br>Language | elaborate /<br>incomprehensible |

| customizable /<br>inconvenient   | Tools<br>System      | feature rich /<br>predetermined |

| economic /<br>unoptimzed         |                      | optimized /<br>uneconomic       |

|                                  |                      |                                 |

|                                  |                      |                                 |

I am about here

Minimal Operating System

### **1. CASE STUDY MINOS**

## **Focus Topics**

- Hardware platform

- Cross development

- Simple modular OS

- Runtime Support

- Realtime task scheduling

- I/O (SPI, UART)\*

- Filesystem (flash disk)

Learn to Know the Target Architecture

### **1.1 HARDWARE**

# ARM Processor Architecture Family

- 32 bit Reduced Instruction Set Computer architecture by ARM Holdings

- 1st production 1985 (Acorn Risc Machine at 4MHz)

- ARM Ltd. today does not sell hardware but (licenses for) chip designs

- StrongARM

- by DEC & Advanced Risc Machines.

- XScale implementation by Intel (now Marvell) after DEC take over

- More than 90 percent of the sold mobile phones (since 2007) contain at least one ARM processor (often more)\* [95% of smart phones, 80% of digital cameras and 35% of all electronic devices\*]

- Modular approach: ARM families produced for different profiles, such as Application Profile, Realtime Profile and Microcontroller / Low Cost Profile

## ARM Architecture Versions

|              |                                                                                                    | VFPv3/v4                 |                                                                 |

|--------------|----------------------------------------------------------------------------------------------------|--------------------------|-----------------------------------------------------------------|

| Architecture | Features                                                                                           | NEON™<br>Adv SIMD        | Key fe<br>ARM<br>compa                                          |

| ARM v1-3     | Cache from ARMv2a,<br>32-bit ISA in 26-bit address space                                           | Thumb <sup>o</sup> -2    | A32+T32 ISAs<br>including: in                                   |

| ARM v4       | Pipeline, MMU,<br>32 bit ISA in 32 bit address space                                               | SIMD<br>VFPv2            | Scalar FP     SP and DP)     Adv SIMD     SP Float)     AArch32 |

| ARM v4T      | 16-bit encoded<br>Thumb Instruction Set                                                            | ARMv5 ARMv6 ARMv7-A/R    | ARMv8-,                                                         |

| ARM v5TE     | Enhanced DSP instructions, in particular for audio processing                                      |                          |                                                                 |

| ARM v5TEJ    | Jazelle Technology extension to su<br>technology (documentation restricted                         | ••                       |                                                                 |

| ARM v6       | SIMD instructions, Thumb 2, Multic Extension                                                       | ore, Fast Context Switch | ٦                                                               |

| ARM v7       | profiles: Cortex- A (applications), -F (microcontroller)                                           | R (real-time), -M        |                                                                 |

| ARM v8       | Supports 64-bit data / addressing (<br>Assembly language overview availa<br>instruction semantics) | • ,                      | les pure                                                        |

CRYPTO CRYPTO

### ARM Processor Families

very simplified & sparse

| Architecture        | Product Line / Family (Implementation) | Speed (MIPS)        |

|---------------------|----------------------------------------|---------------------|

| ARMv1-ARMv3         | ARM1-3, 6                              | 4-28 (@8-33MHz)     |

| ARMv3               | ARM7                                   | 18-56 MHz           |

| ARMv4T, ARMv5TEJ    | ARM7TDMI                               | up to 60            |

| ARMv4               | StrongARM                              | up to 200 (@200MHz) |

| ARMv4               | ARM8                                   | up to 84 (@72MHz)   |

| ARMv4T              | ARM9TDMI                               | 200 (@180MHz)       |

| ARMv5TE(J)          | ARM9E                                  | 220(@200MHz)        |

| ARMv5TE(J)          | ARM10E                                 |                     |

| ARMv5TE             | XScale                                 | up to 1000 @1.25GHz |

| ARMv6               | ARM11                                  | 740                 |

| ARMv6, ARMv7, ARMv8 | ARM Cortex                             | up to 2000 (@>1GHz) |

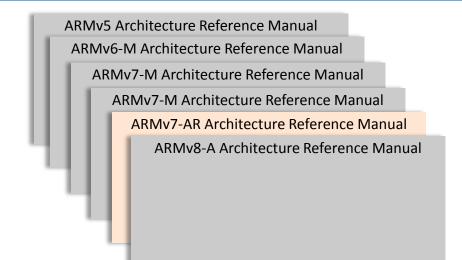

## **ARM Architecture Reference Manuals**

#### describe

- ARM/Thumb instruction sets

- processor modes and states

- exception and interrupt model

- system programmer's model, standard coprocessor interface

- memory model, memory ordering and memory management for different potential implementations

- (optional) extensions like Floating Point, SIMD, Security, Virtualization ...

for example required for the implementation of assembler, disassembler, compiler, linker and debugger and for the systems programmer.

## **ARM Technical System Reference Manuals**

#### describe

- particular processor implementation of an ARM architecture

- redundant information from the Architecture manual (e.g. system control processor)

- additional processor implementation specifics

(e.g. cache sizes and cache handling, interrupt controller, generic timer)

usually required by a system's programmer

Cortex<sup>™</sup>-A7 MPCore<sup>™</sup> Technical Reference Manual

## System on Chip Implementation Manuals

#### describe

- particular implementation of a System on Chip

- address map: physical addresses and bit layout for the registers

- peripheral components / controllers, such as Timers, Interrupt controller, GPIO, USB, SPI, DMA, PWM, UARTs

usually required by a system's programmer.

BCM2835 ARM Peripherals

## **ARM Instruction Set**

#### consists of

- Data processing instructions

- Branch instructions

- Status register transfer instructions

- Load and Store instructions

- Generic Coprocessor instructions

- Exception generating instructions

of the ARM Instruction Set

- 32 bit instructions / many in one cycle / 3 operands

- Load / store architecture (no memory operands such as in x86)

ldr r11, [fp, #-8] add r11, r11, #1 str r11, [fp, #-8]

increment a local variable

of the ARM Instruction Set

Index optimized instructions (such as pre-/post-indexed addressing)

stmdb sp!,{fp,lr}; store multiple decrease before and update sp

stack activation frame

Idmia sp!,{fp,pc} ; load multiple decrease after and update sp

of the ARM Instruction Set

Predication: all instructions can be conditionally executed\*

cmp r0, #0. swieq #0xa

of the ARM Instruction Set

bl #0x0a0100070

Link Register

## procedure call

Shift and rotate in instructions

add r11, fp, r11, lsl #2

r11 = fp + r11\*4 e.g. array access

of the ARM Instruction Set

PC-relative addressing

Idr r0, [pc, #+24]Ioad a largeconstant

Coprocessor access instructions

mrc p15, 0, r11, c6, c0, 0 • • • setup the mmu

#### ARM Instruction Set Encoding (ARM v5)

|                                                          | 31 30 29 28 | 27262 | 5 2 | 423 | 22   | 2120 | 19 18 17 16 | 15 14 13 12 | 11 10 9 8      | 7 6 5                 | 4   | 3 2 1 0 | 19 |                                      |

|----------------------------------------------------------|-------------|-------|-----|-----|------|------|-------------|-------------|----------------|-----------------------|-----|---------|----|--------------------------------------|

| Data processing immediate shift                          | cond [1]    | 000   |     | орс | ode  | S    | Rn          | Rd          | shift amou     | int shi <del>ft</del> | 0   | Rm      |    |                                      |

| Miscellaneous instructions:<br>See Figure 3-3            | cond [1]    | 000   | ) 1 | 0   | x    | x 0  | x           | x           | x              | x x x                 | 0   | x       |    | shiftable register                   |

| Data processing register shift [2]                       | cond [1]    | 0 0 0 | )   | орс | ode  | s    | Rn          | Rd          | Rs             | 0 shift               | 1   | Rm      |    |                                      |

| Miscellaneous instructions:<br>See Figure 3-3            | cond [1]    | 000   |     | ٥   | ¥    | × 0  | x           | x           | x              | 0 x x                 | 1   | x       |    |                                      |

| Multiplies, extra load/stores:<br>See Figure 3-2         | cond [1]    | 000   | x   | x   | x    | хx   | x           | x           | x              | 1 x x                 | 1   | x       |    | conditional execution                |

| Data processing immediate [2]                            | cond [1]    | 0 0   | 1   | орс | ode  | s    | Rn          | Rd          | rotate         | _in                   | nme | diate   |    | Q kit imme edietee with              |

| Undefined instruction [3]                                | cond [1]    | 00    | 1   | 0   | x    | 0 0  | x           | x           | x              | x x x                 | x   | x x x x |    | 8 bit immediates with<br>even rotate |

| Move immediate to status register                        | cond [1]    | 0 0 1 | 1   | 0   | R    | 1 0  | Mask        | SBO         | rotate         | im                    | nme | diate   |    | load / store with                    |

| Load/store immediate offset                              | cond [1]    | 010   | P   | U   | вv   | V L  | Rn          | Rd          |                | immedia               | te  |         |    | destination increment                |

| Load/store register offset                               | cond [1]    | 0 1 1 | F   | U   | ВV   | NL   | Rn          | Rd          | shift amou     | nt shift              | 0   | Rm      | 1  |                                      |

| Undefined instruction                                    | cond [1]    | 0 1 1 | x   | x   | x    | x x  | x           | <u> </u>    | <u>v v v v</u> | 1 10 metersa          |     |         |    | undefined instruction:               |

| Undefined instruction [4,7]                              | 1 1 1 1     | 0 x x | x   | x   | х    | хх   | x x x x     | x x x x     | x x x x        | ххх                   | х   | x x x x |    | user extensibility                   |

| Load/store multiple                                      | cond [1]    | 100   | ) F | U   | sv   | N L  | Rn          |             | regis          | ter list              |     |         |    | load / store with multiple           |

| Undefined instruction [4]                                | 1 1 1 1     | 100   | x   | x   | х    | x x  | x x x x     | x x x x     | хххх           | ххх                   | х   | x x x x |    | registers                            |

| Branch and branch with link                              | cond [1]    | 1 0 1 | L   | 8   |      |      |             | 24-bit      | offset         | _                     | _   |         |    | huan ah ao with 24 hit               |

| Branch and branch with link<br>and change to Thumb [4]   | 1 1 1 1     | 101   | н   |     |      |      |             | 24-bit      | offset         | E.                    |     |         |    | branches with 24 bit<br>offset       |

| Coprocessor load/store and double register transfers [6] | cond [5]    | 1 1 0 | F   | U   | N    | WL   | Rn          | CRd         | cp_num         | 8-                    | bit | offset  |    |                                      |

| Coprocessor data processing                              | cond [5]    | 1 1 1 | 0   | 0   | pcod | de1  | CRn         | CRd         | c <u>p num</u> | opcode2               | 0   | CRm     |    | generic coprocessor<br>instructions  |

| Coprocessor register transfers                           | cond [5]    | 1 1 1 | 0   | ор  | code | e1 L | CRn         | Rd          | cp_num         | opcode2               | 1   | CRm     |    |                                      |

| Software interrupt                                       | cond [1]    | 1 1 1 | 1   |     |      |      |             | swi ni      | umber          |                       |     |         | ē. |                                      |

| Undefined instruction [4]                                | 1 1 1 1     | 1 1 1 | 1   | x   | x    | x x  | x           | x x x x     | x x x x        | x x x                 | х   | x x x x |    |                                      |

# **Thumb Instruction Set**

ARM instruction set complemented by

- Thumb Instruction Set

- 16-bit instructions, 2 operands

- eight GP registers accessible from most instructions

- subset in functionality of ARM instruction set

- targeted for density from C-code (~65% of ARM code size)

- Thumb2 Instruction Set

- extension of Thumb, adds 32 bit instructions to support almost all of ARM ISA (different from ARM instruction set encoding!)

- design objective: ARM performance with Thumb density

#### Other Contemporary RISC Architectures

Examples

- MIPS (MIPS Technologies)

- Business model similar to that of ARM

- Architectures MIPS(I|...|V), MIPS(32|64), microMIPS(32|64)

- AVR (Atmel)

- Initially targeted towards microcontrollers

- Harvard Architecture designed and Implemented by Atmel

- Families: tinyAVR, megaAVR, AVR32

- AVR32: mixed 16-/32-bit encoding

- SPARC (Sun Microsystems)

- Available as open-source: e.g. LEON (FPGA)

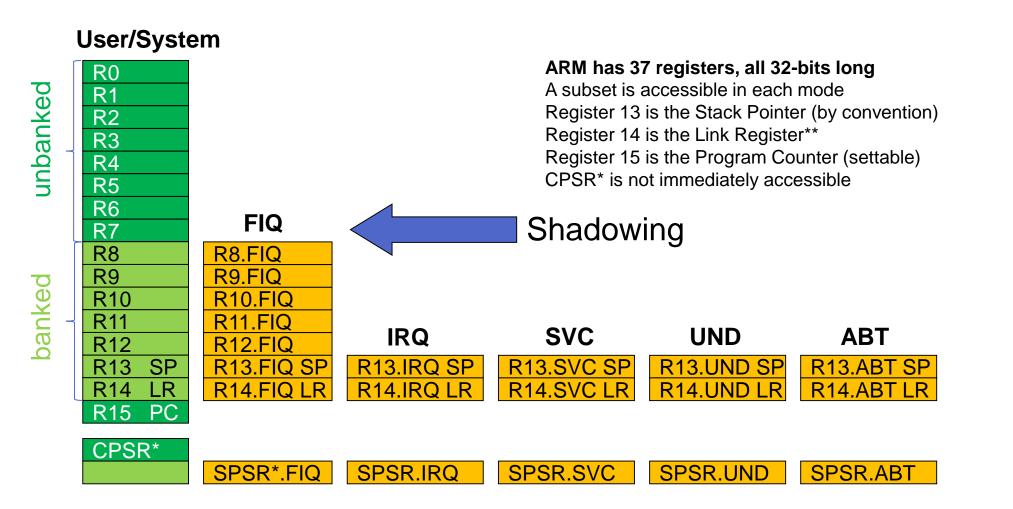

## **ARM Processor Modes**

- ARM from v5 has (at least) seven basic operating modes

- Each mode has access to **own stack** and a different subset of registers

- Some operations can only be carried out in a privileged mode

| Mode       | Description / Cause                                 |        |

|------------|-----------------------------------------------------|--------|

| Supervisor | Reset / Software Interrupt                          |        |

| FIQ        | Fast Interrupt                                      | exc    |

| IRQ        | Normal Interrupt                                    | ⊢ epti |

| Abort      | Memory Access Violation                             | ions   |

| Undef      | Undefined Instruction                               |        |

| System     | Privileged Mode with same registers as in User Mode | noi    |

| User       | Regular Application Mode                            | cution |

## **ARM Register Set**

\* current / saved processor status register, accessible via MSR / MRS instructions \*\* more than a convention: link register set as side effect of some instructions

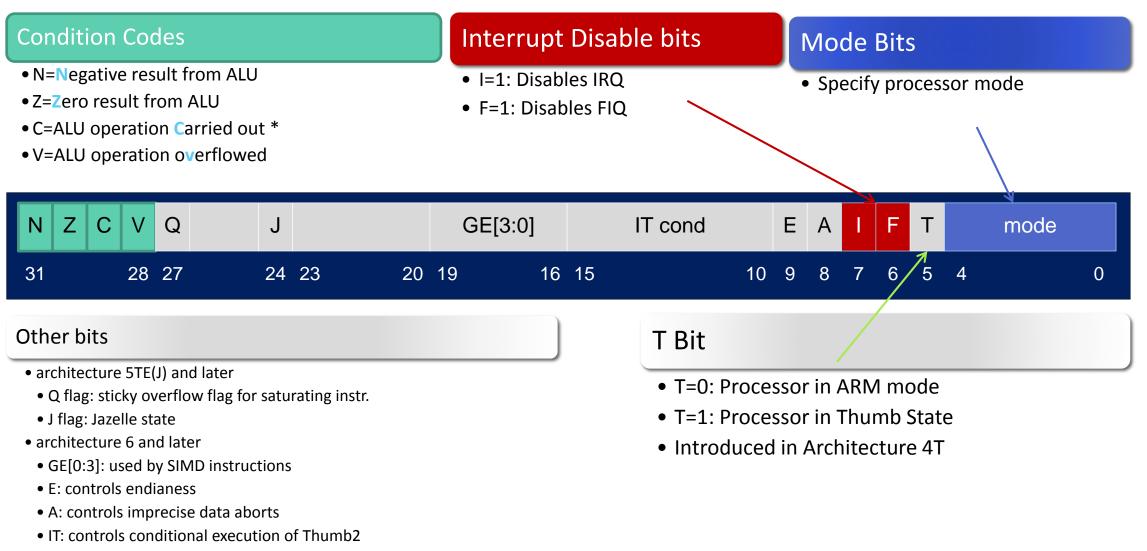

## Processor Status Register (PSR)

# Typical procedure call on ARM

| Caller: push parameters                                                                        | •••                               |                             |         |

|------------------------------------------------------------------------------------------------|-----------------------------------|-----------------------------|---------|

| use branch and link instruction. Stores the PC of the next instruction into the link register. | bl #address                       | ()                          | stack g |

| <b>Callee:</b> save link register and frame pointer on stack and set new frame pointer.        | stmdb sp!, {fp, lr}<br>mov fp, sp | parameters<br>Ir<br>prev fp | rows    |

| Execute procedure content                                                                      | ••••                              | ριεντρ                      |         |

| Reset stack pointer and restore frame pointer and and jump back to caller address.             | mov sp, fp<br>Idmia sp!, {fp, pc} | local<br>vars               |         |

| Caller: cleanup parameters from stack                                                          | add sp, sp, #n                    |                             |         |

|                                                                                                | • • •                             |                             |         |

#### 34

## **Exceptions (General)**

Exception = abrupt change in the control flow as a response to some change in the processor's state

- Interrupt asynchronous event triggered by a device signal

- Trap / Syscall intentional exception

- Fault error condition that a handler might be able to correct

- Abort error condition that cannot be corrected

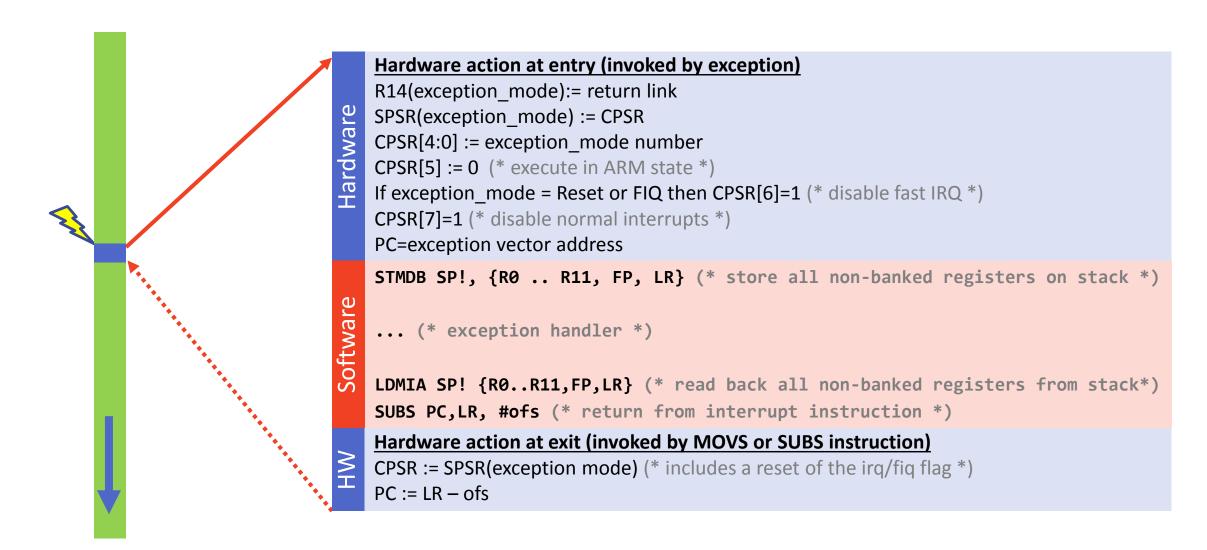

## **Exception Handling**

Involves close interaction between hardware and software.

Exception handling is similar to a procedure call with important differences:

- processor prepares exception handling: save\* part of the current processor state before execution of the software exception handler

- assigned to each exception is an exception number, the exception handler's code is accessible via some exception table that is configurable by software

- exception handlers run in a different processor mode with complete access to the system resources.

## Exception Table on ARM

| Туре                  | Mode       | Address* | return link(type)** |

|-----------------------|------------|----------|---------------------|

| Reset                 | Supervisor | 0x0      | undef               |

| Undefined Instruction | Undefined  | 0x4      | next instr          |

| SWI                   | Supervisor | 0x8      | next instr          |

| Prefetch Abort        | Abort      | 0xC      | aborted instr +4    |

| Data Abort            | Abort      | 0x10     | aborted instr +8    |

| Interrupt (IRQ)       | IRQ        | 0x18     | next instr +4       |

| Fast Interrupt (FIQ)  | FIRQ       | 0x1C     | next instr +4       |

\* alternatively High Vector Address = 0xFFFF0000 + adr (configurable)

\*\* different numbers in Thumb instruction mode

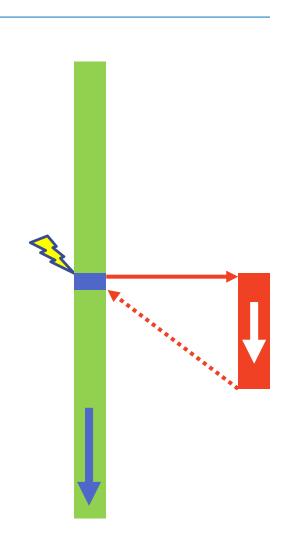

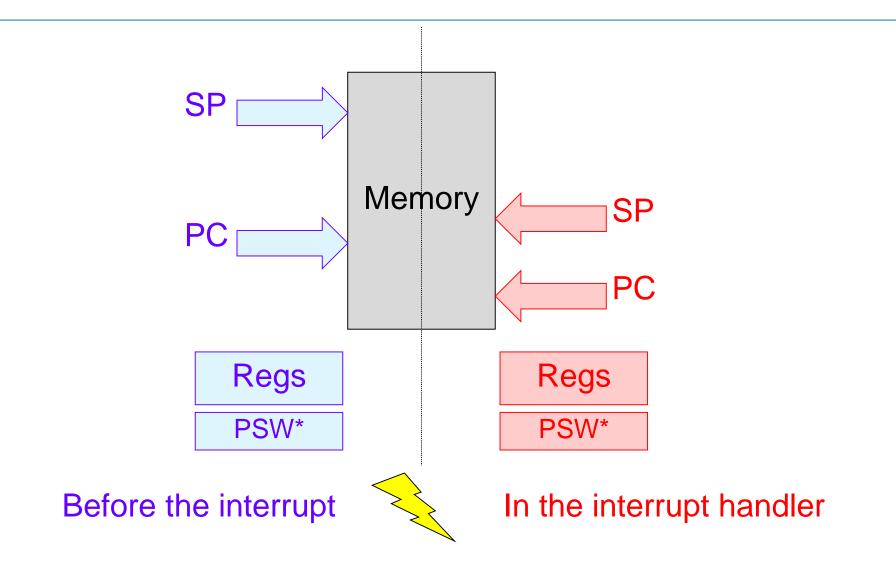

## Context change, schematic

# Exception handling on ARM

# Raspberry Pi 2

- Raspberry Pi 2 will be the hardware used at least in the first 4 weeks lab sessions

- Produced by element14 in the UK (www.element14.com)

- Features

- Broadcom BCM2836 ARMv7 Quad Core Processor running at 900 MHz

- 1G RAM

- 40 PIN GPIO

- Separate GPU ("Videocore")

- Peripherals: UART, SPI, USB, 10/100 Ethernet Port (via USB), 4pin Stereo Audio, CSI camera, DSI display, Micro SD Slot

- Powered from Micro USB port

## ARM System Boot

- ARM processors usually starts executing code at adr 0x0

- e.g. containing a branch instruction to jump over the interrupt vectors

- usually requires some initial setup of the hardware

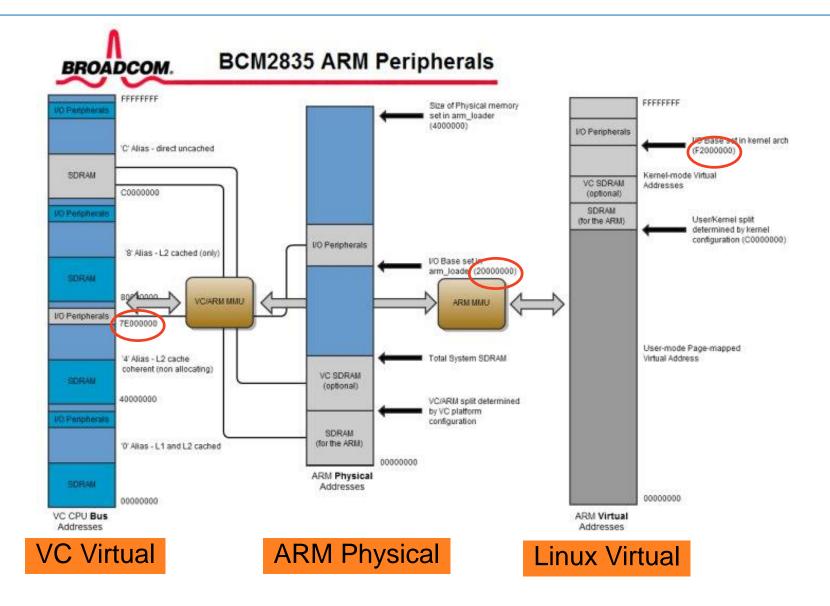

- The RPI, however, is booted from the Video Core CPU (VC): the firmware of the RPI does a lot of things before we get control: kernel-image gets copied to address 0x8000H and branches there No virtual to physical address-translation takes place in the beginning.

- Only one core runs at that time. (More on this later)

## **RPI 1 Memory Map**

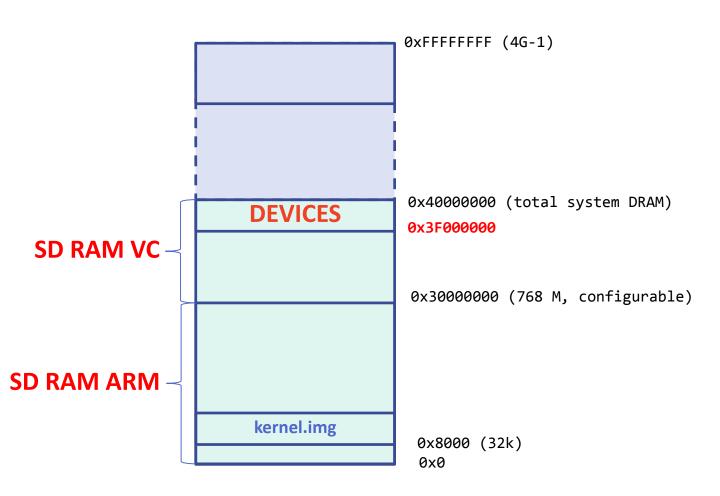

## RPI 2 Memory Map

- Initially the MMU is switched off. No memory translation takes place.

- System memory divided in ARM and VC part, partially shared (e.g. frame buffer)

- ARM's memory mapped registers start from 0x3F000000

-- opposed to reported offset 0x7E000000 in BCM 2835

Manual

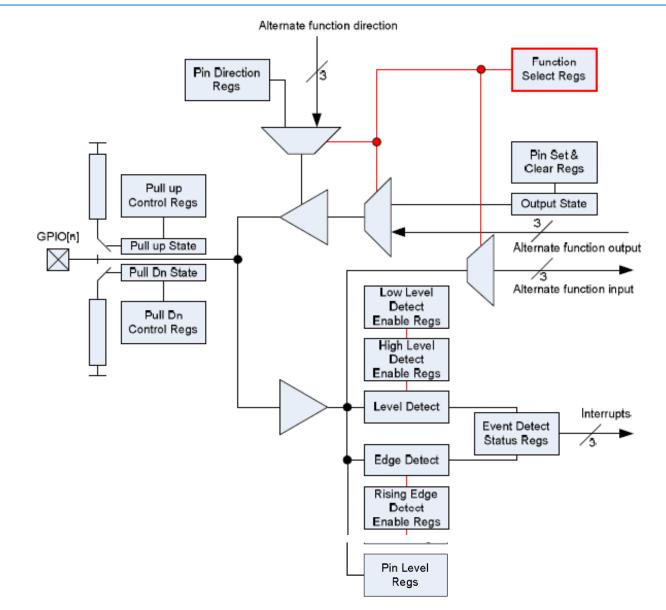

#### General Purpose I/O (GPIO)

- Software controlled processor pins

- Configurable direction of transfer

- Configurable connection

- → with internal controller (SPI, MMC, memory controller, ...)

- → with external device

- Pin state settable & gettable

- High, low

- Forced interrupt on state change

- On falling/ rising edge

#### **GPIO** Block Diagram (BCM 2835)

## Raspberry Pi 2 GPIO Pinout

|                | name           | pin |     | pin | name        |  |

|----------------|----------------|-----|-----|-----|-------------|--|

|                | 3.3 V DC       | 01  | ••  | 02  | DC power 5v |  |

|                | GPIO 02        | 03  | • • | 04  | DC power 5v |  |

|                | GPIO 03        | 05  | ••  | 06  | ground      |  |

| Hade In the UK | GPIO 04        | 07  | ••  | 08  | GPIO 14     |  |

|                | ground         | 09  | • • | 10  | GPIO 15     |  |

|                | <b>GPIO 17</b> | 11  | ••  | 12  | GPIO 18     |  |

|                | <b>GPIO 27</b> | 13  | ••  | 14  | ground      |  |

|                | <b>GPIO 22</b> | 15  | ••  | 16  | GPIO 23     |  |

|                | 3.3V DC        | 17  | • • | 18  | GPIO 24     |  |

|                | GPIO 10        | 19  | ••  | 20  | ground      |  |

|                | GPIO 09        | 21  | ••  | 22  | GPIO 25     |  |

|                | GPIO 11        | 23  | ••  | 24  | GPIO 08     |  |

|                | ground         | 25  | • • | 26  | GPIO 07     |  |

|                | ID_SD          | 27  | ••  | 28  | ID_SC       |  |

|                | <b>GPIO 05</b> | 29  | ••  | 30  | ground      |  |

|                | GPIO 06        | 31  | ••  | 32  | GPIO 12     |  |

|                | <b>GPIO 13</b> | 33  | ••  | 34  | ground      |  |

|                | GPIO 19        | 35  | ••  | 36  | GPIO 16     |  |

|                | GPIQ 26        | 37  | ••  | 38  | GPIO 20     |  |

|                | ground         | 39  | • • | 40  | GPIO 21     |  |

## **Documentation Examples**

| Addr               | ess    | Field Name |                       | Description    |                                                                                                               |         |            |                                                                                                                      | Read/<br>Write                                                               |                                                                      |      |       |

|--------------------|--------|------------|-----------------------|----------------|---------------------------------------------------------------------------------------------------------------|---------|------------|----------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------|----------------------------------------------------------------------|------|-------|

| <del>0x 7E20</del> | 0000   | GPFSEL0    | GPIO Fun              | ction Select 0 |                                                                                                               |         |            |                                                                                                                      | RW                                                                           | -                                                                    |      |       |

| 0x 7E20            | 0000   | GPFSEL0    | GPIO Fun              | ction Select 0 |                                                                                                               |         |            | 32                                                                                                                   | R/W                                                                          |                                                                      |      |       |

| 0x 7E20            | 0004   | GPFSEL1    | GPIO Fun              | ction Select 1 |                                                                                                               | Bit(s)  | Field Name | Description                                                                                                          |                                                                              |                                                                      | Туре | Reset |

| 0x 7E20            | 8000 0 | GPFSEL2    | GPIO Fun              | ction Select 2 |                                                                                                               | 31-30   |            | Reserved                                                                                                             |                                                                              |                                                                      | R    | 0     |

| 0x 7E20            | 000C   | GPFSEL3    |                       | ction Select 3 |                                                                                                               | 29-27   | FSEL19     | <u>FSEL19 - Function</u><br>000 = GPIO Pin 1<br>001 = GPIO Pin 1                                                     | 19 is an input<br>19 is an output                                            |                                                                      | R/W  | 0     |

| 0x 7E20            | 0 0010 | GPESEI 4   | GPIO Fun              | ction Select A |                                                                                                               |         |            | 100 = GPIO Pin 1<br>101 = GPIO Pin 1<br>110 = GPIO Pin 1<br>111 = GPIO Pin 1<br>011 = GPIO Pin 1<br>010 = GPIO Pin 1 | 19 takes alterna<br>19 takes alterna<br>19 takes alterna<br>19 takes alterna | ate function 1<br>ate function 2<br>ate function 3<br>ate function 4 |      |       |

| 1                  | GEIOTO | LUW        |                       | 305            | <1 <del>0</del>                                                                                               | 26-24   | FSEL18     | FSEL18 - Functio                                                                                                     | on Select 18                                                                 |                                                                      | R/W  | 0     |

|                    | GPIO14 | Low        | TXD0                  | SD6            | <re< td=""><td>served&gt;</td><td></td><td></td><td></td><td>TXD1</td><td></td><td>0</td></re<>               | served> |            |                                                                                                                      |                                                                              | TXD1                                                                 |      | 0     |

|                    | GPIO15 | Low        | RXD0                  | SD7            | <re< td=""><td>served&gt;</td><td></td><td></td><td></td><td>RXD1</td><td></td><td>0</td></re<>               | served> |            |                                                                                                                      |                                                                              | RXD1                                                                 |      | 0     |

| -                  | GPIO16 | Low        | <reserved></reserved> | SD8            | <re< td=""><td>served&gt;</td><td>CTSC</td><td>SPI1_C</td><td>E2_N</td><td>CTS1</td><td></td><td>0</td></re<> | served> | CTSC       | SPI1_C                                                                                                               | E2_N                                                                         | CTS1                                                                 |      | 0     |

| ł                  | 00017  | Low        | records               | 600            | -10                                                                                                           | convod- | ртес       | CDH C                                                                                                                | NET N                                                                        | DTet                                                                 | I    | 0     |

|                    |        |            |                       |                |                                                                                                               | 8-6     | FSEL12     | FSEL12 - Functio                                                                                                     | on Select 12                                                                 |                                                                      | R/W  | 0     |

|                    |        |            |                       |                |                                                                                                               | 5-3     | FSEL11     | FSEL11 - Function                                                                                                    | on Select 11                                                                 |                                                                      | R/W  | 0     |

|                    |        |            |                       |                |                                                                                                               | 2-0     | FSEL10     | FSEL10 - Functio                                                                                                     | on Select 10                                                                 |                                                                      | R/W  | 0     |

Table 6-3 – GPIO Alternate function select register 1

# GPIO Setup (RPI2)

Program GPIO Pin Function (in / out / alternate function) by writing corresponding (memory mapped) GPFSEL register. GPFSELn: pins 10\*n .. 10\*n+9 Use RMW (Read-Modify-Write) operation in order to keep the other bits

2. Use GPIO Pin

- a. If writing: set corresponding bit in the GPSETn or GPCLRn register set pin: GPSETn: pins 32\*n .. 32\*n+31 clear pin: GPCLRn: pins 32\*n .. 32\*n+31 no RMW required.

- b. If reading: read corrsponding bit in the GPLEVn register GPLEVn: pins 32\*n ... 32\*n+1

- c. If "alternate function": device acts autonomously. Implement device driver.